Multiplexer is simply a data selector.It has multiple inputs and one output.Any one of the input line is transferred to output depending on the control signal.This type of operation is usually referred as multiplexing .In 8:1 multiplexer ,there are 8 inputs.Any of these inputs are transferring to output ,which depends on the control signal.For 8 inputs we need ,3 bit wide control signal .

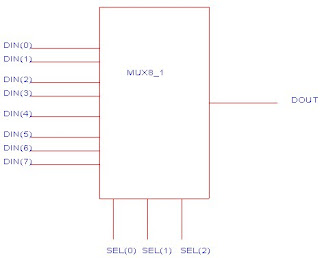

Working:If control signal is "000" ,then the first input is transferring to output line.If control signal is "111",then the last input is transferring to output.Similarly for all values of control signals.A simple block diagram of 8:1 multiplexer is shown here.

Now see the VHDL code of 8:1 multiplexer

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY MUX8_1 IS

PORT(DIN:IN STD_LOGIC_VECTOR(7 DOWNTO 0);SEL:IN STD_LOGIC_VECTOR(2 DOWNTO 0);DOUT:OUT STD_LOGIC);

END MUX8_1;

ARCHITECTURE BEH123 OF MUX8_1 IS

BEGIN

PROCESS(DIN,SEL)

BEGIN

CASE SEL IS

WHEN"000"=>DOUT<=DIN(0);

WHEN"001"=>DOUT<=DIN(1);

WHEN"010"=>DOUT<=DIN(2);

WHEN"011"=>DOUT<=DIN(3);

WHEN"100"=>DOUT<=DIN(4);

WHEN"101"=>DOUT<=DIN(5);

WHEN"110"=>DOUT<=DIN(6);

WHEN"111"=>DOUT<=DIN(7);

WHEN OTHERS=>

DOUT<='Z';

END CASE;

END PROCESS;

END BEH123;

Tuesday 21 September 2010

VHDL MODEL OF 8:1(8 INPUT) MULTIPLEXER

06:07

VHDL

Contact us

<<===POST YOUR COMMENTS HERE & MENTION THE POST LINK===>>

foxyform